(查看詳細產品說明書,敬請點擊商鋪左側“友情鏈接”【奎克半導體簡體中文網站 】進入奎克公司網站,在瀏覽 器地址欄公司網址後續接“/QA84727.htm”進行查閱)

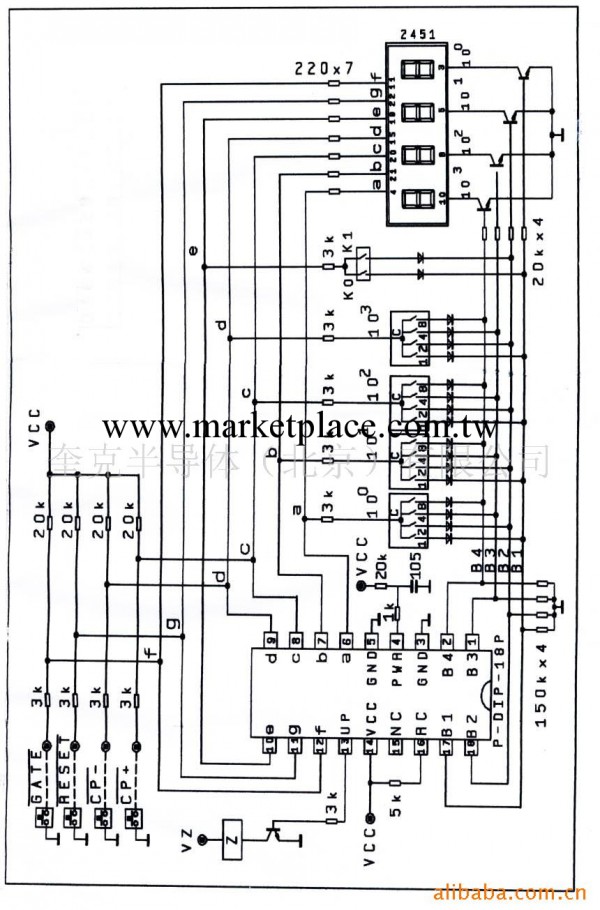

4位數顯,碼盤整定,循環計數,加減可逆,高抗幹擾,掉電保持高速電路QA641828,QA645828 低速高抗擾 雙時鐘可逆計數電路(下沿)上行:碼盤設定終值(初值為零) ■(查看詳細產品說明書,敬請點擊商鋪左側“友情鏈接”進入奎克公司網站,在瀏覽器地址欄公司網址後續接“/QA84727.htm”進行查閱。) ● 18腳雙列直插或SOIC貼片封裝。 ● 四位數字顯示。直接驅動共陰LED,無需外接譯碼器。帶高位無效“0”消隱。 ● 四位碼盤整定。(碼盤缺省為“0”。四位全“0”,片內置為全“9”) ● 由K1,K0選擇四種倍率∶×1,×10,×100,×1000。 ● 具門控累計積算功能,GATE開關on時計數暫停。 ● 具片內上電復位電路和外接手動復位電路。外接手動復位低電平有效。RESET開關低電平寬度必須大於20mS才為有效, 從而增強電路的抗擾能力。 ● 加計數電路初值為零、終值為碼盤值,從初值加計數至終值時符合。 ● 減計數電路終值為零、初值為碼盤值,從初值減計數至終值時符合。 ● 可逆計數電路計數輸入端“CP+”的下沿產生加計數,“CP-”的下沿產生減計數。上行電路碼盤值為終值(初值為零),下行電路碼盤值為初值(終值為零)。計數從初值開始,無論加、減,使計數值等於終值時符合。 計數可循環,即:“0000”減1為“9999”,“9999”加1為“0000”。 ● 對於無任何後綴的普通型電路, 當計數達到終值符合時,符合輸出端“UP”從“0”上跳為“1”,並禁止繼續計數。 ● 對於有後綴“B”的電路, 隻要計數值大於等於碼盤值,符合輸出端“UP ”就為“1”電平,小於碼盤值時則為“0”電平,但始終不禁止計數。 ● 對於有後綴“CT”的電路, 當計數達到終值符合時, 符合輸出端“UP”輸出電平取反(復位後為“0”), 計數值自動復位並重新從初值開始計數。 ● 對於有後綴“CP”的電路, 當計數達到終值符合時, 符合輸出端“UP”輸出一個正脈沖,計數值自動復位並重新從初值開始計數。輸出端常態為“0”電平。 ●QA64X828,/B/CT/CP/CE,(-W)的計數輸入端COUNT、CP+、CP-下沿計數(計數開關“on”),對應型號中X為1、2、3、4、5、6電路輸入端口分別具有1、2、3、4、5、50毫秒的抗擾、防抖電路,最小正、負脈寬分別對應為≥1、2、3、4、5、50毫秒,最高計數頻率分別對應為500HZ、250HZ、150HZ、125HZ、100HZ、10HZ。 ● 以上電路帶有後綴“-W”的, 為具有掉電低功耗數據保持功能的電路(保持電流典型值0.1μA)。 《低功耗保持功能》 掉電低功耗數據保持電路的連接見圖2、圖4、圖6。當主電V+掉電後, 芯片僅需由備電VB提供最多5μA的保持電流(典型值0.1μA)。VB 與 V+ 無嚴格要求, V+電壓應略高於VB電壓,確保正常情況下由V+供電而VB不消耗電流,且應使VCC端電壓符合VCC電源范圍要求。在低功耗保持期間, 芯片能記憶當時已進行的計數狀態。為降低芯片功耗,除電源測試端PUB仍為輸入端外, 其它全部入出端口均變為輸出口且輸出“0”電平。 當V+ 恢復供電時, 在PUB端產生一個負脈沖,使芯片從掉電時刻狀態起繼續工作。 因從V+恢復供電到芯片各輸入端恢復為輸入態約需2mS時間,為避免瞬時短路,需接高電平的輸入端應通過最小0.5K的上拉電阻接V+, 避免直接接電源。因V+掉電後電路會自動轉入低功耗數據保持狀態,且所需電流極微,VCC 端的殘電或許會較長時間維持電路處於記憶狀態, 所以如果需要使用斷電再上電的方法使電路復位,則不僅需斷掉V+和VB電源,而且還要確保將VCC端的殘電泄放幹凈。 ■價格見“價格索引”D檔

批發市場僅提供代購諮詢服務,商品內容為廠商自行維護,若有發現不實、不合適或不正確內容,再請告知我們,查實即會請廠商修改或立即下架,謝謝。